Publications

Author key underline: Students advised; *: communication authors; ^: co-first author.2026

-

Autonomous Evolution of EDA Tools: Multi-Agent Self-Evolved ABC

Cunxi Yu and Haoxing Ren

Design Automation Conference (DAC 2026) -

TOPCELL: Topology Optimization of Standard Cell via LLMs

Zhan Song, Yu-Tung Liu, Chen Chen, Guoheng Sun, Jiaqi Yin, Chia-tung Ho, Ang Li, Haoxing Ren, and Cunxi Yu

Design Automation Conference (DAC 2026) -

SchemaCoder: Automatic Log Schema Extraction Coder with Residual Q-Tree Boosting

Jiaxin Wan, Chia-tung Ho, Rongjian Liang, Cunxi Yu, Deming Chen, and Haoxing Ren

Design Automation Conference (DAC 2026) -

ReVEAL: GNN-Guided Reverse Engineering for Formal Verification of Optimized Multipliers

Chen Chen, Daniela Kaufmann, Chenhui Deng, Hongce Zhang, and Cunxi Yu

International Conference on Tools and Algorithms for the Construction and Analysis of Systems (TACAS 2026) -

FVRuleLearner: Operator-Level Reasoning Tree (Op-Tree)-Based Rules Learning for Formal Verification

Jiaxin Wan, Chia-tung Ho, Yunsheng Bai, Cunxi Yu, Deming Chen, and Haoxing Ren

44th IEEE VLSI Test Symposium (VTS) -

A Scalable Lift-and-Project Differentiable Approach For the Maximum Cut Problem

Ismail Alkhouri, Mian Wu, Cunxi Yu, Jia Liu, Rongrong Wang, and Alvaro Velasquez

AISTATS 2026

2025

-

Autonomous Code Evolution Meets NP-Completeness

Cunxi Yu, Rongjian Liang, Chia-Tung Ho, Haoxing Ren

arXiv:2509.07367

-

e-boost: Boosted E-Graph Extraction with Adaptive Heuristics and Exact Solving

Jiaqi Yin, Zhan Song, Chen Chen, Yaohui Cai, Zhiru Zhang, and Cunxi Yu

ACM/IEEE International Conference on Computer-Aided Design (ICCAD'25) (Best Paper Nomination) -

Revisit Choice Network for Synthesis and Technology Mapping

Chen Chen, Jiaqi Yin, and Cunxi Yu

ACM/IEEE International Conference on Computer-Aided Design (ICCAD'25) -

GROOT: Graph Edge Re-growth and Partitioning for the Verification of Large Designs in Logic Synthesis

Kiran Thorat, Hongwu Peng, Yuebo Luo, Xi Xie, Shaoyi Huang, Amit Hasan, Jiahui Zhao, Yingjie Li, Zhijie Shi, Cunxi Yu, and Caiwen Ding

ACM/IEEE International Conference on Computer-Aided Design (ICCAD'25) -

Mapping Fusion: Improving FPGA Technology Mapping with ASIC Mapper

Cunxi Yu

ACM/IEEE Workshop on Machine Learning for CAD (MLCAD'25) -

Optimizing CUDA Graph Scheduling with Reinforcement Learning: A Case Study in SSTA Propagation

Cheng-Hsiang Chiu, Chedi Morchdi, Chih-Chun Chang, Cunxi Yu, Yi Zhou, and Tsung-wei Huang

ACM/IEEE Workshop on Machine Learning for CAD (MLCAD'25) -

ASPEN: LLM-Guided E-Graph Rewriting for RTL Datapath Optimization

Niansong Zhang, Chenhui Deng, Johannes Maximilian Kuehn, Chia-Tung Ho, Cunxi Yu, Zhiru Zhang, and Haoxing Ren

ACM/IEEE Workshop on Machine Learning for CAD (MLCAD'25) HEC: Equivalence Verification Checking for Code Transformation via Equliaty Saturation

Jiaqi Yin, Zhan Song, Nicolas Bohm Agostini, Antonino Tumeo, and Cunxi Yu

USENIX Annual Technical Conference (ATC'25)Optical Neural Engine for Solving Scientific Partial Differential Equations

Yingheng Tang, Ruiyang Chen, Minhan Lou, Jichao Fan, Cunxi Yu, Andy Nonaka, Zhi Yao, Weilu Gao

Nature Communications

BoolE: Exact Symbolic Reasoning via Boolean Equality Saturation

Jiaqi Yin, Zhan Song, Chen Chen, Qihao Hu and Cunxi Yu

Design Automation Conference (DAC'25) (Best Paper Nomination, 5/1862)

GitHub

GitHub

E-morphic: Scalable Equality Saturation for Structural Exploration in Logic Synthesis

Chen Chen, Guangyu Hu, Cunxi Yu, Yuzhe Ma and Hongce Zhang

Design Automation Conference (DAC'25)

GitHub

GitHub

Differentiable Quadratic Optimization For the Maximum Independent Set Problem

Ismail Alkhouri, Cedric Le Denmat, Yingjie Li, Cunxi Yu, Jia Liu, Rongrong Wang, Alvaro Velasquez

International Conference on Machine Learning (ICML'25)

GitHub

GitHub

SmoothE: Differentiable E-Graph Extraction

Yaohui Cai, Kaixin Yang, Chenhui Deng, Cunxi Yu, Zhiru Zhang

Architectural Support for Programming Languages and Operating Systems (ASPLOS'25) (Best Paper Award)

GitHub

GitHub

Digitized Phase Change Material Heterostack for Diffractive Optical Neural Network

Ruiyang Chen, Cunxi Yu, Weilu Gao

Advanced Photonics Research (2025)

SGSS: Streaming 6-DoF Navigation of Gaussian Splat Scenes

Mufeng Zhu, Mingju Liu, Cunxi Yu, Cheng-Hsin Hsu, Yao Liu

ACM 16th 2025 Multimedia Systems Conference (MMsys'25).

2024

MapTune: Advancing ASIC Technology Mapping via Reinforcement Learning Guided Library Tuning

Mingju Liu, Daniel Robinson, Yingjie Li, Cunxi Yu

IEEE/ACM International Conference On Computer Aided Design (ICCAD'24)

GitHub

GitHub

Differentiable Combinatorial Scheduling at Scale

Mingju Liu^, Yingjie Li^, Jiaqi Yin, Zhiru Zhang, Cunxi Yu

International Conference on Machine Learning (ICML'24)

GitHub

GitHub

Linear Algebra Approach to Verification of Modular (2^n−1) Multipliers

Jiteshri Dasari, Cunxi Yu, Maciej Ciesielski

2024 IFIP/IEEE 32nd International Conference on Very Large Scale Integration (VLSI-SoC)

E-Syn: E-Graph Rewriting with Technology-Aware Cost Functions for Logic Synthesis

Chen Chen, Guangyu Hu, Dongsheng Zuo, Cunxi Yu, Yuzhe Ma and Hongce Zhang

Design Automation Conference (DAC'24) GitHub

GitHub

Less is More: Hop-wise Graph Attention for Scalable and Generalizable Learning on Circuits

Chenhui Deng, Zichao Yue, Cunxi Yu, Gokce Sarar, Ryan Carey, Rajeev Jain and Zhiru Zhang

Design Automation Conference (DAC'24) GitHub

GitHub

FPGA EDA: Design Principles and Implementation

Kaihui Tu , Xifan Tang , Cunxi Yu, Lana Josipović , Zhufei Chu

Springer (Book), 2024BoolGebra: Attributed Graph-learning for Boolean Algebraic Manipulation

Yingjie Li, Anthony Agnesina, Yanqing Zhang, Mark Ren, Cunxi Yu

IEEE Design, Automation and Test in Europe Conference (DATE'24)

DAG-aware Synthesis Orchestration

Yingjie Li, Mingju Liu, Alan Mishchenko, Mark Ren, Cunxi Yu

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)

orchestrate@ABC

orchestrate@ABC

2023

Accelerating Exact Combinatorial Optimization via RL-based Initialization -- A Case Study in Scheduling

Jiaqi Yin, Cunxi Yu

ACM/IEEE International Conference on Computer-Aided Design (ICCAD'23)

Verilog-to-PyG -- A Framework for Graph Learning and Augmentation on RTL Designs

Yingjie Li, Mingju Liu, Alan Mishchenko, Cunxi Yu

ACM/IEEE International Conference on Computer-Aided Design (ICCAD'23)

Verilog-to-PyG

Verilog-to-PyG

AIM: Accelerating Arbitrary-precision Integer Multiplication on Heterogeneous Reconfigurable Computing Platform Versal ACAP

Zhuoping Yang, Jinming Zhuang, Jiaqi Yin, Cunxi Yu, Alex Jones and Peipei Zhou

ACM/IEEE International Conference on Computer-Aided Design (ICCAD'23)

GitHub

GitHub

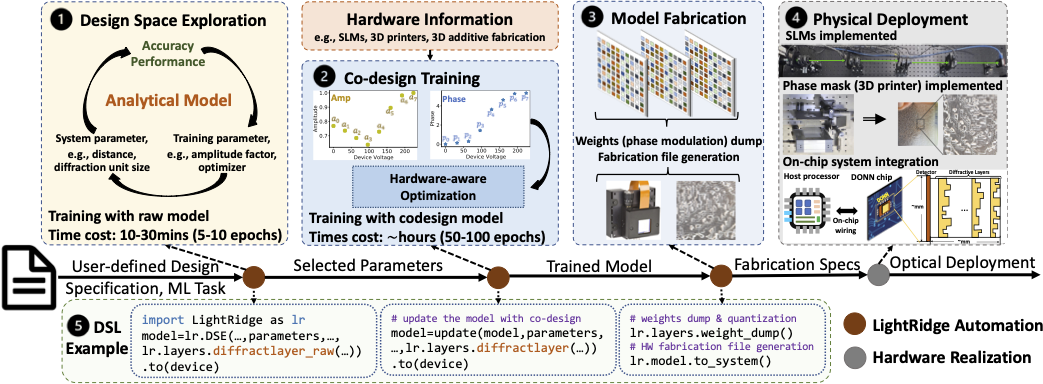

LightRidge: An End-to-end Agile Design Framework for Diffractive Optical Neural Networks

Yingjie Li, Ruiyang Chen, Minhan Lou, Berardi Sensale-Rodriguez, Weilu Gao, Cunxi Yu

ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS'24)

LightRidge

LightRidge

RubikONNs: Multi-task Learning with Rubik's Diffractive Optical Neural Networks

Yingjie Li, Weilu Gao*, Cunxi Yu*

32nd International Joint Conference on Artificial Intelligence (IJCAI'23) (15%)

Github (LightRidge)

Github (LightRidge)

Invited: Equality Saturation for Datapath Synthesis: A Pathway to Pareto Optimality

Ecenur Ustun, Cunxi Yu, and Zhiru Zhang

Design Automation Conference (DAC'23) (Invited Perspective Paper)RESPECT: Reinforcement Learning based Edge Scheduling on Pipelined Coral Edge TPUs

Jiaqi Yin, Yingjie Li, Daniel Robinson, Cunxi Yu

Design Automation Conference (DAC'23) (23%)

GitHub

GitHub

Gamora: Graph Learning based Symbolic Reasoning for Large-Scale Boolean Networks

Nan Wu, Yingjie Li, Steve Dai, Cong (Callie) Hao, Cunxi Yu*, Yuan Xie

Design Automation Conference (DAC'23) (23%) (Best Paper Award, 2/1157)

GitHub

GitHub

SlidesPhysics-aware Roughness Optimization for Diffractive Optical Neural Networks

Shanglin Zhou^, Yingjie Li^, Minhan Lou, Weilu Gao, Cunxi Yu, Caiwen Ding

Design Automation Conference (DAC'23) (23%)

Github: will be released with LightRidge

Github: will be released with LightRidge

Tutorial: A Journey to Optical Computing: From Physics Fundamentals to Hardware-Software Co-Design, Automation, and Application

Jiaqi Gu, Chenghao Feng, Hanqing Zhu, Ray T. Chen, Ulf Schlichtmann, Zhengqi Gao, Duane Boning, Yingjie Li, Cunxi Yu

Design Automation Conference (DAC'23)

SlidesTutorial: Reinforcing Circuit and Layout Synthesis

Shubham Rai, Cunxi Yu, Huigang Liao, Keren Zhu

Design Automation Conference (DAC'23)

Book chapter: Machine Learning for Agile FPGA Design

Debjit Pal, Chenhui Deng, Ecenur Ustun, Cunxi Yu, Zhiru Zhang

Springer (Book: Machine Learning Applications in Electronic Design Automation, Haoxing Ren, Jiang Hu.)Effects of Interlayer Reflection and Interpixel Interaction in Diffractive Optical Neural Networks

Minhan Lou, Yingjie Li, Cunxi Yu, Berardi Sensale-Rodriguez, Weilu Gao*

Optics Letter. Jan 2023.

2022

Device-system Co-design of Photonic Neuromorphic Processor using Reinforcement Learning

Yingheng Tang, Princess Tara Zamani, Ruiyang Chen, Jianzhu Ma, Minghao Qi, Cunxi Yu*, Weilu Gao*

Laser & Photonics Reviews. Oct 2022. (IF:13.2)

FlowTune: End-to-end Automatic Logic Optimization Exploration via Domain-specific Multi-armed Bandi

Walter Lau Neto, Yingjie Li, Pierre-Emmanuel Gaillardon, Cunxi Yu

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD'22)

GitHubPhysics-aware Complex-valued Adversarial Machine Learning in Reconfigurable Diffractive All-optical Neural Network

Ruiyang Chen^, Yingjie Li^, Minhan Lou, Jichao Fan, Yingheng Tang, Berardi Sensale-Rodriguez, Cunxi Yu*, Weilu Gao*

Laser & Photonics Reviews. Vol 16, July 2022 (IF:13.2).

Physics-aware Differentiable Discrete Codesign for Diffractive Optical Neural Networks

Yingjie Li, Ruiyang Chen, Weilu Gao and Cunxi Yu.

IEEE/ACM International Conference On Computer Aided Design (ICCAD'22) (22%), Nov. 2022.

Invited: Physics-aware Adversarial Machine Learning: An Experimental Study in Diffractive Optical Neural Networks

Yingjie Li, Ruiyang Chen, Minhan Lou, Jichao Fan, Yingheng Tang, Berardi Sensale-Rodriguez, Weilu Gao, Cunxi Yu

Invited talk at workshop 3rd ROAD4NN@Design Automation Conference (DAC '22).

Talk@YouTube

Pre-print

LightRidge: An Open-source Compiler Framework for Diffractive Optical ML Architectures

Yingjie Li, Ruiyang Chen, Minhan Lou, Berardi Sensale-Rodriguez, Weilu Gao and Cunxi Yu.

First Workshop on Open-Source Computer Architecture Research (OSCAR) held in conjunction with ISCA (ISCA'49), June 2022.Exact Memory- and Communication-aware Scheduling of DNNs on Pipelined Edge TPUs

Jiaqi Yin, Zhiru Zhang, and Cunxi Yu

ACM/IEEE Symposium on Edge Computing (SEC'22) (17%). Seattle, WA, December 5-8, 2022IMpress: Large Integer Multiplication Expression Rewriting for FPGA HLS

Ecenur Ustun, Ismail San, Jiaqi Yin, Cunxi Yu, and Zhiru Zhang

Talk@YouTube

International Symposium on Field-Programmable Custom Computing Machines (FCCM'22) (21%).Physics-informed Recurrent Neural Network for Time Dynamics in Optical Resonances

Yingheng Tang, Jichao Fan, Xinwei Li, Jianzhu Ma, Minghao Qi, Cunxi Yu*, Weilu Gao*

Nature Computational Science

Github

Github

Combinatorial RL-based Scheduling for Pipelined Edge TPUs

Jiaqi Yin, Yingjie Li, Cunxi Yu

TinyML Research Symposium 2022 (TinyML'22)Physics-informed Neural Network for Forecasting Time-domain Signals in Terahertz Resonances.

Tang, Yingheng, Jichao Fan, Xinwei Li, Jianzhu Ma, Minghao Qi, Cunxi Yu, and Weilu Gao.

Conference on Lasers and Electro-Optics (CLEO'22).Complex-valued Reconfigurable Diffractive Optical Neural Networks using Cost-effective Spatial Light Modulators

Ruiyang Chen, Yingjie Li, Minhan Lou, Cunxi Yu, Weilu Gao

Conference on Lasers and Electro-Optics (CLEO'22).DLS Best Poster Honorable Mention, American Physics Society

2021

Real-time Multi-Task Learning in Diffractive Deep Neural Networks via Hardware-Software Co-design

extended version @ arXiv

Yingjie Li, Ruiyang Chen, Berardi Sensale Rodriguez, Weilu Gao*, Cunxi Yu*

Nature Scientific Reports(see demo video below)

Physical Adversarial Attacks of Diffractive Deep Neural Networks

Yingjie Li, Cunxi Yu

IEEE/ACM 58th Design Automation Conference (DAC 2021).SLAP: A Supervised Learning Approach for Priority Cuts Technology Mapping

[ Github]

Github]

Walter Lau Neto, Matheus Trevisan Moreira, Yingjie Li, Luca Amaru, Cunxi Yu, and Pierre-Emmanuel Gaillardon

IEEE/ACM 58th Design Automation Conference (DAC 2021).Graphene Optoelectronic Artificial Intelligence Accelerators

Weilu Gao*, Cunxi Yu, Ruiyang Chen

Conference on Lasers and Electro-Optics (CLEO), Virtual Conference, May. 11-13, 2021.

Artificial Intelligence Accelerators based on Graphene Optoelectronic Devices

Weilu Gao, Cunxi Yu, Ruiyang Chen

Advanced Photonics Research

Read your Circuit: Leveraging Word Embedding to Guide Logic Optimization

[ Github]

Github]

Walter Lau Neto, Matheus Trevisan Moreira, Luca Amaru, Cunxi Yu, and Pierre-Emmanuel Gaillardon

IEEE/ACM 26th Asia and South Pacific Design Automation Conference (ASP-DAC 2021).

2020

Decision Making in Synthesis cross Technologies using LSTMs and Transfer Learning [Github] [Talk]

Cunxi Yu, Wang Zhou

2nd ACM/IEEE Workshop on Machine Learning for CAD (MLCAD) 16-20 November, 2020.FlowTune: Practical Multi-armed Bandits in Boolean Optimization

[ Github] [Talk]

Github] [Talk]

Cunxi Yu

IEEE/ACM International Conference On Computer Aided Design (ICCAD'20), Nov. 2020.EaSyOpt: Predicting Post Place and Route Critical Paths for Early Synthesis Optimization

Walter Lau Neto*, Matheus Trevisan Moreira, Luca Amaru, Cunxi Yu, and Pierre-Emmanuel Gaillardon

IWLS 2020. Virtual

2019

Understanding Algebraic Rewriting for Arithmetic Circuit Verification: a Bit-Flow Model

Github

Maciej Ciesielski, Tiankai Su, Atif Yasin, Cunxi Yu

Github

Maciej Ciesielski, Tiankai Su, Atif Yasin, Cunxi Yu

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)LAMDA: Learning-Assisted Multi-Stage Autotuning for FPGA Design Closure [Talk]

Ecenur Ustun, Shaojie Xiang, Jinny Gui, Cunxi Yu, and Zhiru Zhang.

IEEE Symp. on Field Programmable Custom Computing Machines (FCCM), 2019.- Painting on Placement: Forecasting Routing Congestion using Conditional Generative Adversarial Nets [GIF Link] [Slides]

Cunxi Yu, Zhiru Zhang

ACM/IEEE Design Automation Conference (DAC'19)

-

Spectral Approach to Verifying Non-linear Arithmetic Circuits [Algebraic Spectrum Gallery & Github]

Cunxi Yu, Atif Yasin, Tiankai Su and Maciej Ciesielski

ACM/IEEE Asia and South Pacific Design Automation Conference (ASP-DAC'19) -

Performance Estimation of Synthesis Flows cross Technologies using LSTMs and Transfer Learning

Cunxi Yu, Wang Zhou

arXiv preprint:1811.06017 [cs.LG] -

Algorithmic Obfuscation over GF($2^m$)

Cunxi Yu, Daniel Holcomb

arXiv preprint:1809.06207 [cs.CR]

2018

-

Rewriting Environment for Arithmetic Circuit Verification [Github]

Cunxi Yu, Atif Yasin, Tiankai Su, Alan Mishchenko and Maciej Ciesielski

International Conference on Logic Programming and Automated Reasoning (LPAR-22) vol 57, pages 656--666.2019 -

Developing Synthesis Flows without Human Knowledge [Datasets & Demo @Github] [Slides]

Cunxi Yu, Houping Xiao and Giovanni De Micheli

ACM/IEEE Design Automation Conference (DAC'18) -

End-to-End Industrial Study of Retiming

Cunxi Yu, Chau-Chin Huang, Gi-Joon Nam, Mihir Choudhury, Victor N. Kravets, Andrew Sullivan, Maciej Ciesielski, Giovanni De Micheli

2018 IEEE Computer Society Annual Symposium on VLSI (ISVLSI'18) -

Generating Safety Guidance for Medical Injection with Three-Compartment Pharmacokinetics Model

Cunxi Yu, Heinz Riener, Francesca Stradolini, Giovanni De Micheli

2018 IEEE Computer Society Annual Symposium on VLSI (ISVLSI'18)

-

Formal Analysis of Galois Field Arithmetic - Parallel Verification and Reverse Engineering [Github] [Benchmarks] [arXiv]

Cunxi Yu, Maciej Ciesielski

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. (TCAD'18) 10.1109/TCAD.2018.2808457 -

Fast Algebraic Rewriting based on And-Inv-Graphs [Github]

Cunxi Yu, Maciej Ciesielski and Alan Mishchenko

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. (TCAD'18) 10.1109/TCAD.2017.2772854 -

Survey on applications of formal methods in reverse engineering and intellectual property protection

Shahrzad Keshavarz, Cunxi Yu, Samaneh Ghandali, Xiaolin Xu, Daniel Holcomb

2018 Journal of Hardware and Systems Security (HaSS'18) -

Computer Algebraic Approach to Verification and Debugging of Galois Field Multipliers

Tiankai Su, Atif Yasin, Cunxi Yu, Maciej Ciesielski

IEEE International Symposium on Circuits and System (ISCAS'18) IEEE, May 2018

2017

-

Advanced Datapath Synthesis using Graph Isomorphism [Slides]

Cunxi Yu, Mihir Choudhury, Andrew Sullivan and Maciej Ciesielski

2017 International Conference On Computer Aided Design (ICCAD'17), Nov. 13 - 16, 2017, Irvine, CA, USA. -

Formal Verification of Truncated Multipliers using Algebraic Approach

Tiankai Su, Cunxi Yu, Atif Yasin, and Maciej Ciesielski

2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI'17), July 3-5, 2017, Bochum, Germany -

Advanced Logic synthesis of Datapaths using Graph Isomorphism

Cunxi Yu, Mihir Choudhury, David Geiger, Andrew Sullivan and Maciej Ciesielski

IWLS 2017, June 2016, Austin, USA. -

Reverse Engineering Irreducible Polynomial of GF(2^m) Arithmetic (Benchmarks)

Cunxi Yu, Daniel Holcomb and Maciej Ciesielski

IEEE/ACM/EDAA Design, Automation and Test in Europe (DATE'17), March 2017. Lausanne, Switzerland

-

Efficient Parallel Verification of Galois Field Multipliers. (Best Paper Nomination) (Benchmarks)

Cunxi Yu and Maciej Ciesielski

IEEE/ACM 22nd Asia and South Pacific Design Automation Conference (ASP-DAC'17), Jan. 16-19, Chiba/Tokyo, Japan.

2016

-

Formal Verification of Arithmetic Circuits by Function Extraction. [Tool] [Benchmarks](Best Paper Nomination)

Cunxi Yu, Walter Brown, Duo Liu, Andre Rossi , Maciej Ciesielski.

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. (TCAD'16) 10.1109/TCAD.2016.2547898 -

Incremental SAT-based Reverse Engineering of Camouflaged Logic Circuits. [Project Web] [Source code] [Benchmarks]

Cunxi Yu, Xiangyu Zhang, Duo Liu, Maciej Ciesielski, Daniel Holcomb.

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. (TCAD'16) -

Formal Verification using Don’t-care and Vanishing Polynomials.

Cunxi Yu and Maciej Ciesielski

2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI'16) , July 2016, Pittsburgh, PA, USA -

Analyzing Imprecise Adders using BDDs - A Case Study.

Cunxi Yu and Maciej Ciesielski

2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI'16) , July 2016, Pittsburgh, PA, USA -

DAG-Aware Logic synthesis of Datapaths (Corrected version).

Cunxi Yu, Mihir Choudhury, Andrew Sullivan and Maciej Ciesielski

IEEE/ACM 53rd Design Automation Conference (DAC'16), June 2016, Austin, USA. -

Automatic Word-level Abstraction on Datapaths.

Cunxi Yu and Maciej Ciesielski

IEEE International Symposium on Circuits and System (ISCAS'16) IEEE, May 2016, Montreal, Canada. -

Oracle-Guided Incremental SAT Solving to Reverse Engineer Camouflaged Logic Circuits.

Duo Liu, Cunxi Yu and Daniel Holcomb

IEEE/ACM/EDAA Design, Automation and Test in Europe (DATE'16), March 2016, Dresden, Germany.

2015

- Logic Debugging of Arithmetic Circuits.

Samaneh Ghandali, Cunxi Yu, Duo Liu, Maciej Ciesielski

2015 IEEE Computer Society Annual Symposium on VLSI (ISVLSI'15) , July 2015, Montpellier, France.

- Verification of Arithmetic Datapath Designs using Word-level Approach.

Cunxi Yu, Walter. Brown and Maciej. Ciesielski

2015 IEEE International Symposium on Circuits and Systems (ISCAS). May 2015, Lisbon,Portugal.

- Verification of Gate-level Arithmetic Circuits by Function Extraction[Tools + Benchmarks] [Slides]

Maciej Ciesielski, Cunxi Yu, Walter Brown, Duo Liu and Andre Rossi

IEEE/ACM 52nd Design Automation Conference (DAC). June, 2015, San Francisco, CA, USA.

- Diagnosis and Debugging of Arithmetic Circuits

Samaneh Ghandali, Cunxi Yu, Duo Liu, Maciej Ciesielski

IEEE/ACM 52nd Design Automation Conference (DAC-WIP). June, 2015, San Francisco, CA, USA.

- Verification of Sequential Arithmetic Circuit.

Cunxi Yu, Duo Liu, Walter Brown, Samaneh Ghandali, Maciej Ciesielski

IEEE/ACM 52nd Design Automation Conference (DAC-WIP). June, 2015, San Francisco, CA, USA.